Features

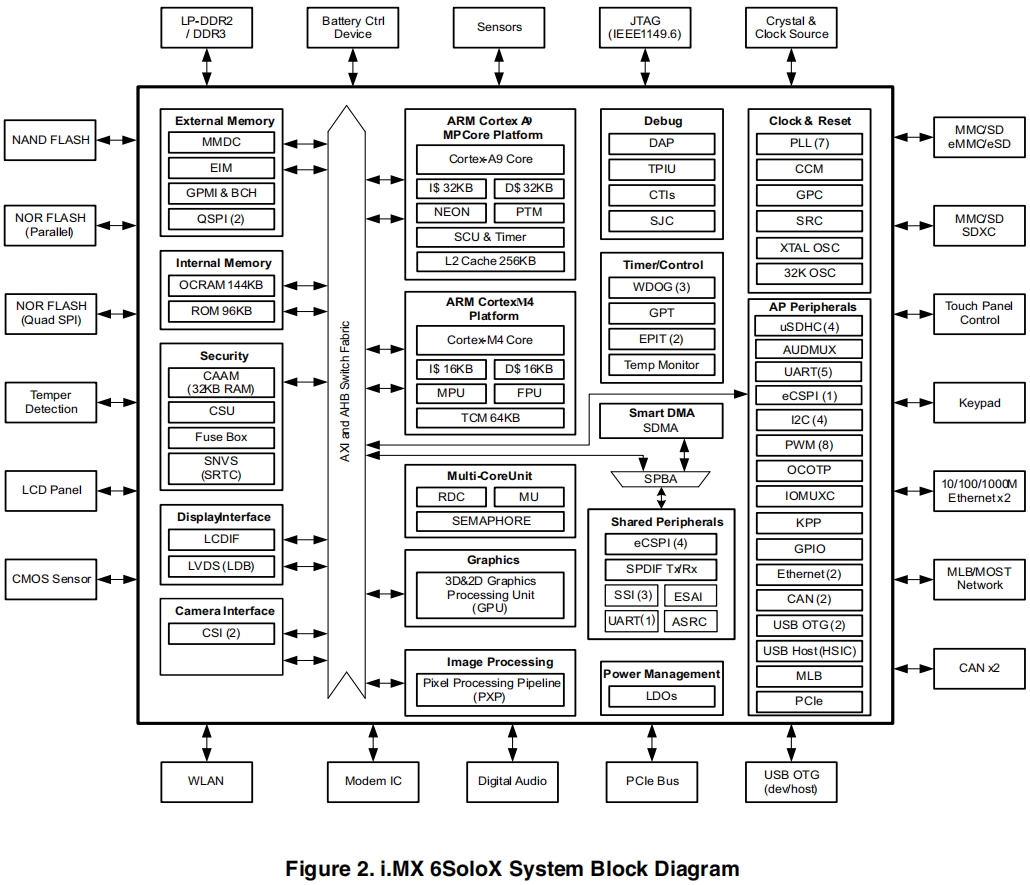

The i.MX 6SoloX processors are based on the Arm Cortex-A9 MPCore™ platform, which has the following features:

• Supports single Arm Cortex-A9 MPCore processor (with TrustZone)

• The core configuration is symmetric, where each core includes:

— 32 KByte L1 Instruction Cache

— 32 KByte L1 Data Cache

— Private Timer and Watchdog

— Cortex-A9 NEON MPE (Media Processing Engine) coprocessor

The Arm Cortex-A9 MPCore complex includes:

• General Interrupt Controller (GIC) with 128 interrupt support

• Global Timer

• Snoop Control Unit (SCU)

• 256 KB unified I/D L2 cache:

• Two Master AXI bus interfaces output of L2 cache

• Frequency of the core (including NEON coprocessor and L1 cache)

• NEON MPE coprocessor

— SIMD Media Processing Architecture

— NEON register file with 32x64-bit general-purpose registers

— NEON Integer execute pipeline (ALU, Shift, MAC)

— NEON dual, single-precision floating point execute pipeline (FADD, FMUL)

— NEON load/store and permute pipeline

— 32 double-precision VFPv3 floating point registers

The Arm Cortex-M4 platform:

• Cortex-M4 CPU core

• MPU (Memory Protection Unit)

• FPU (Floating Point Unit)

• 16 KByte Instruction Cache

• 16 KByte Data Cache

• 64 KByte TCM (Tightly-Coupled Memory)

The SoC-level memory system consists of the following additional components:

— Boot ROM, including HAB (96 KB)

— Internal multimedia / shared, fast access RAM (OCRAM, 128 KB)

— Internal RAM for state retention or general use (OCRAM_S, 16KB)

— Secure/non-secure RAM (32 KB)